使用ModelSim做模拟常常会遇到一些小问题,常常没有很在意但是常常又发生:-),这里谈谈遇到以下几个小问题的解决方法。

1.遇到类似以下的问题:

# ** Error: /homes/ethernet/eth_spram_256x32.v(151): Module 'RAMB4_S8' is not defined.

# **Error: /homes/ethernet/xilinx_dist_ram_16x32.v(20): Module 'RAM16X1D' is not defined.

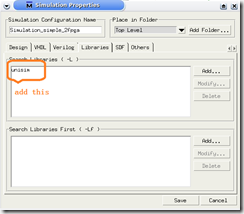

解决方法:进入Simulation Properties: Libraries --> 在Search Libraries中加入unisim(如果是要做 UNISIM-based RTL simulation)

如下图所示:

2.遇到类似以下的问题:

# ** Fatal: (vsim-3693) The minimum time resolution limit (10ps) in the Verilog source is smaller than the one chosen for SystemC or VHDL units in the design. Use the vsim -t option to specify the desired resolution.

# Time: 0 ns Iteration: 0 Instance: /sample_tb File: /homes/sample_tb.vhd Line: UNKNOWN

# FATAL ERROR while loading design

解决方法:改变Simulation Properties: Libraries --> 在Search Libraries中加入unisim(如果是要做 UNISIM-based RTL simulation)

如下图所示:也是进入Simulation Properties,然后如下图所示,改变Resolution。

3.遇到类似以下的问题:

# ** Error: (vsim-3601) Iteration limit reached at time 0 ps.

# ** Note: (vsim-3602) Delays were truncated during elaboration of the design.

解决方法:进入Simulation -> Runtime Options,然后改变Iteration Limit,将它改成例如5000。如下图所示:

没有评论:

发表评论